#### Projet VALMEM

# Démonstration du prototype IMITATOR

Étienne André, Emmanuelle Encrenaz, Laurent Fribourg

Laboratoire Spécification et Vérification

#### Plan

- L'algorithme

- Démonstration sur l'exemple du latch

- Application à SPSMALL

- Travaux futurs

#### Plan

- L'algorithme

- Démonstration sur l'exemple du latch

- Application à SPSMALL

- Travaux futurs

#### Our Method

- Input

- A PTA A with initial state sinit

- An instantiation  $\pi$  of all the parameters of  $\mathcal{A}$

- ★ Exemplifying a good behaviour

- Output : generalisation

- ▶ A constraint *K* on the parameters such that

- $\star \pi \models K$

- \* For all instantiation  $\pi' \models K$ , the set of traces under  $\pi'$  is the same as the set of traces under  $\pi$

## The Algorithm InverseMethod

```

.4 : PTA

Input

\pi_0: Valuation of P

Output K_0: Constraint on the parameters

Variables i : Current iteration

S: Current set of symbolic states (S = Post^{i}_{\Lambda(K)})

S': Former set of symbolic states

K: Current constraint on the parameters

i := 0; K := True; S := \{s_0\}; S' := \{s_0\}

D0

DO UNTIL S is \pi_0-compatible

Select a \pi_0-incompatible state (q, C) of S

Select an inequality J of (\exists X : C) such that \pi_0 \models \neg J

S' := S; K := K \wedge \neg J; S := Post'_{A(K)}

\%\% S \pi_0-compatible

OD

S' := S; S := Post_{A(K)}(S); i := i + 1

IF S = S'

%% S \pi_0-compatible and S = Post^*_{A(K)}

THEN RETURN K_0 := \bigcap_{(a,C) \in S} (\exists X : C)

FΙ

```

OD

## Le prototype IMITATOR

- IMITATOR

- Inverse Method for Inferring Time AbstracT behaviOR

- Programme de 1500 lignes en Python

- Appels à HYTECH pour le calcul du Post

- Appels à Prolog (non essentiels)

- ullet En entrée : un fichier HYTECH contenant une instantiation des paramètres

- En sortie : une contrainte sur les paramètres assurant le même comportement

- Temps de mise au point : environ 2 « Étienne-mois »

#### **Avancement**

- L'algorithme

- Démonstration sur l'exemple du latch

- Application à SPSMALL

- Travaux futurs

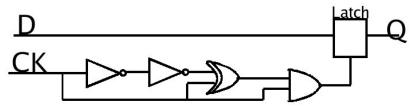

## Rappel du circuit latch

- Cinq éléments :

- Deux portes « non »

- Une porte « ou exclusif »

- Une porte « et »

- Une bascule à niveau (« latch »)

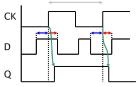

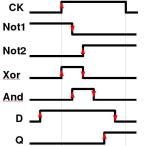

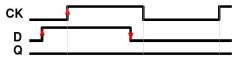

## Signaux

Signaux fournis par Rémy

• Signaux aux différentes portes

#### Modélisation

- Modélisation des portes

- Seules les transitions marquées en rouge sont modélisées

- Ex: l'automate de la porte « not 1 » ne fait que produire un front descendant

- Définition d'un mauvais état

- Un cycle d'horloge complet a eu lieu

- Q n'a pas effectué de front montant

- Utilisation de paramètres

- lacktriangle Exemple : durée de front montant du latch :  $\delta_{\textit{Latch}^\uparrow}$

#### Génération d'une contrainte

• Valeurs des paramètres  $(\pi_0)$  générées par Patricia

Appel à IMITATOR... (en live!)

#### Génération d'une contrainte

• Valeurs des paramètres  $(\pi_0)$  générées par Patricia

- Appel à IMITATOR... (en live!)

- Contrainte  $K_0$  (obtenue après simplification par HYTECH) :

```

\begin{array}{c|c} 0 < \delta_{And} \downarrow \\ \wedge & \delta_{Xor} \uparrow = \delta_{Not1} \downarrow \\ \wedge & \delta_{And} \uparrow + \delta_{Latch} \uparrow < T_{Hold} \\ \wedge & \delta_{Not1} \downarrow + \delta_{Not2} \uparrow < \delta_{And} \uparrow + \delta_{Latch} \uparrow \\ \wedge & T_{Setup} < T_{LO} \\ \wedge & T_{Hold} < \delta_{Not1} \downarrow + \delta_{Not2} \uparrow + \delta_{Xor} \downarrow \\ \wedge & \delta_{Not1} \downarrow + \delta_{Not2} \uparrow + \delta_{Xor} \downarrow + \delta_{And} \downarrow \leq T_{HI} \end{array}

```

### Interprétation des contraintes obtenues

- Interprétation de  $\delta_{And}{}^{\uparrow} + \delta_{Latch}{}^{\uparrow} < T_{Hold}$

- ► Le temps de maintien de D doit être supérieur à la somme des temps maxima du front montant du « and » et de franchissement du latch

## Interprétation des contraintes obtenues

- ullet Interprétation de  $\delta_{\mathit{And}^{\uparrow}} + \delta_{\mathit{Latch}^{\uparrow}} < T_{\mathit{Hold}}$

- ▶ Le temps de maintien de D doit être supérieur à la somme des temps maxima du front montant du « and » et de franchissement du latch

- Minimisation du T<sub>Hold</sub>

- $\blacktriangleright$  Après instanciation de  $K_0$  pour tous les paramètres sauf  $T_{Hold}$

$$320 < T_{Hold} < 718$$

#### **Avancement**

- L'algorithme

- Démonstration sur l'exemple du latch

- Application à SPSMALL

- Travaux futurs

## Application à une portion de SPSMALL

- Portion de SPSMALL

- Modèle généré automatiquement depuis la description des transistors

- Automates temporisés paramétrés et leurs valeurs temporelles fournis d'après simulation par Remy

## Application à une portion de SPSMALL

- Portion de SPSMALL

- Modèle généré automatiquement depuis la description des transistors

- Automates temporisés paramétrés et leurs valeurs temporelles fournis d'après simulation par Remy

- Application de IMITATOR (après semi-instanciation)

- Valeurs initiales des setup

```

T_{setupwen} = 48

T_{setupd} = 108

```

## Application à une portion de SPSMALL

- Portion de SPSMALL

- Modèle généré automatiquement depuis la description des transistors

- Automates temporisés paramétrés et leurs valeurs temporelles fournis d'après simulation par Remy

- Application de IMITATOR (après semi-instanciation)

- Valeurs initiales des setup

$$T_{setupwen} = 48$$

$T_{setupd} = 108$

Contraintes obtenues

$$46 < T_{setupwen} < 54$$

$\land 99 < T_{setupd} < 110$

$\land T_{setupd} < T_{setupwen} + 61$

#### **Avancement**

- L'algorithme

- Démonstration sur l'exemple du latch

- Application à SPSMALL

- Travaux futurs

#### Travaux futurs

- Méthode générant une contrainte imitant exactement le même comportement que les valeurs initiales

- Contrainte trop forte pour notre cas : un circuit peut avoir d'autres bons fonctionnements

- Idée : élargir la zone progressivement par application de la méthode, tant que le mauvais comportement n'est pas atteint

- Passage à l'échelle

- L'usage d'HYTECH empêche de considérer plus de 10 automates (peu!)

- ► Temps bien trop élevé du simple fait d'une spécificité de HYTECH (composition *a priori* des automates)

- ▶ Idée : utilisation d'un autre outil, ou création d'un outil ad hoc

- ▶ Objectif : contrainte sur la mémoire SPSMALL complète